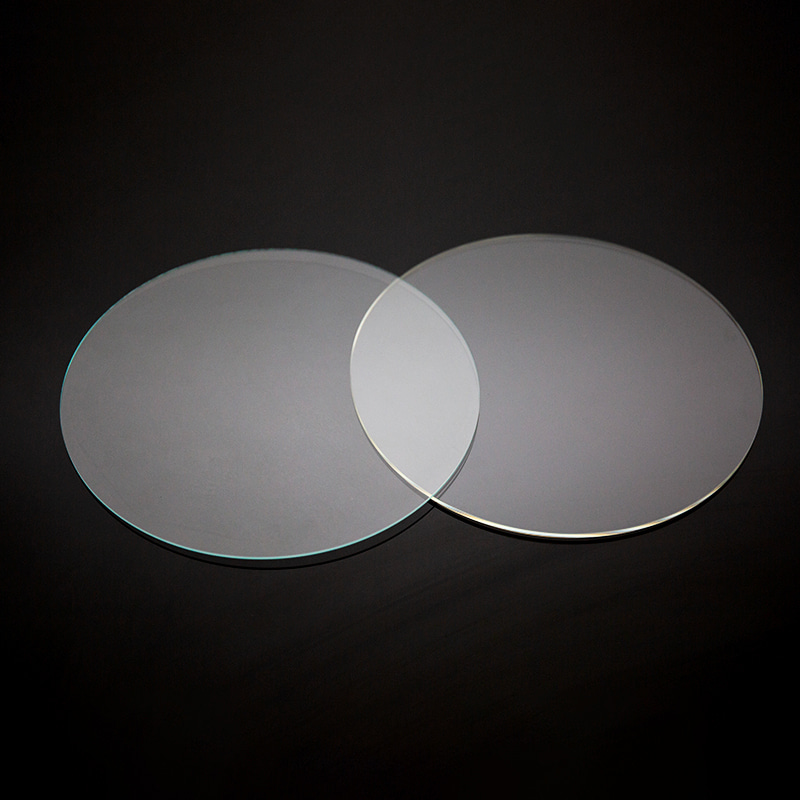

Độ phẳng là một thông số quan trọng trong việc chế tạo các tấm quang học. Tấm quang học đóng vai trò là thành phần cơ bản trong nhiều ứng dụng, bao gồm quang tử học, laser, cảm biến quang học và hệ thống thấu kính có độ chính xác cao. Bất kỳ sai lệch nào so với độ phẳng đều có thể làm giảm hiệu suất của thiết bị, gây ra quang sai quang học và giảm năng suất sản xuất. Do đó, việc đảm bảo độ phẳng của tấm wafer là điều cần thiết để duy trì cả chất lượng và chức năng.

Hiểu độ phẳng của wafer quang học

Độ phẳng của tấm bán dẫn quang học đề cập đến tính đồng nhất của bề mặt tấm bán dẫn dọc theo mặt phẳng của nó. Những sai lệch so với mặt phẳng lý tưởng có thể xảy ra dưới dạng cong, vênh hoặc gợn sóng bề mặt. Những biến thể này có thể được đo bằng cách sử dụng một số tham số, bao gồm tổng biến thiên độ dày, cấu hình bề mặt và số liệu độ phẳng tổng thể. Thông thường, độ phẳng được biểu thị bằng micromet, với dung sai chặt chẽ hơn cần thiết cho các ứng dụng quang học có độ chính xác cao.

Tầm quan trọng của độ phẳng xuất phát từ nhu cầu truyền ánh sáng có thể dự đoán được qua tấm bán dẫn. Ngay cả những sai lệch bề mặt nhỏ cũng có thể làm biến dạng chùm ánh sáng, làm giảm hiệu suất laser hoặc làm hỏng lớp phủ quang học. Do đó, độ phẳng không chỉ là thước đo chất lượng mà còn là yêu cầu về chức năng.

Các yếu tố ảnh hưởng đến độ phẳng của wafer quang

Một số yếu tố ảnh hưởng đến độ phẳng của wafer trong quá trình chế tạo. Những yếu tố này có thể được phân loại rộng rãi thành tính chất vật liệu, xử lý cơ học và điều kiện môi trường.

Thuộc tính vật liệu

Việc lựa chọn vật liệu đóng một vai trò quan trọng trong độ phẳng của tấm wafer. Tấm quang học thường được làm từ vật liệu tinh thể như silicon, gali arsenide hoặc sapphire, mỗi loại có đặc tính cơ học và nhiệt độc đáo. Sự khác biệt về hệ số giãn nở nhiệt, ứng suất bên trong và khuyết tật tinh thể có thể gây ra cong vênh. Ví dụ, sự giãn nở dị hướng trong các tấm bán dẫn tinh thể có thể gây ra hiện tượng cong nếu tấm bán dẫn không được định hướng đúng dọc theo trục tinh thể.

Gia công cơ khí

Các bước xử lý cơ học, bao gồm cắt, mài và đánh bóng, ảnh hưởng trực tiếp đến độ phẳng của tấm bán dẫn. Việc cắt một tinh thể từ một bó hoa sẽ tạo ra các ứng suất cơ học có thể làm cong tấm bán dẫn. Tương tự, hoạt động mài loại bỏ vật liệu để đạt được độ dày mong muốn nhưng có thể gây ra sự phân bố ứng suất không đồng đều. Đánh bóng, cần thiết cho chất lượng bề mặt quang học, có thể khắc phục một số sai lệch này nếu được thực hiện cẩn thận nhưng cũng có thể gây ra hiện tượng uốn cong vi mô nếu không được kiểm soát đúng cách.

Điều kiện môi trường

Các yếu tố môi trường, chẳng hạn như nhiệt độ, độ ẩm và độ rung, ảnh hưởng đến độ phẳng của tấm bán dẫn. Trong quá trình chế tạo, tấm bán dẫn có thể hấp thụ độ ẩm hoặc chịu sự chênh lệch nhiệt độ, gây biến dạng tạm thời hoặc vĩnh viễn. Duy trì môi trường phòng sạch được kiểm soát là điều cần thiết để giảm thiểu những tác động này và duy trì độ phẳng.

Kỹ thuật đảm bảo độ phẳng

Đảm bảo độ phẳng trong chế tạo tấm bán dẫn quang học bao gồm sự kết hợp giữa lựa chọn vật liệu, xử lý chính xác và đo lường. Một số kỹ thuật thường được sử dụng để đạt được và kiểm tra độ phẳng.

1. Lựa chọn vật liệu cẩn thận

Bước đầu tiên để đảm bảo độ phẳng của tấm wafer là lựa chọn nguyên liệu thô chất lượng cao. Các bó hoa không được có khuyết tật bên trong và được định hướng cẩn thận để giảm thiểu tác động dị hướng. Sử dụng tinh thể có ứng suất thấp giúp giảm khả năng cong vênh trong quá trình cắt và xử lý tiếp theo.

2. Cắt lát chính xác

Cắt lát wafer liên quan đến việc cắt các tấm wafer mỏng từ tinh thể khối bằng cách sử dụng cưa dây hoặc lưỡi dao được phủ kim cương. Cắt chính xác làm giảm căng thẳng cơ học bằng cách duy trì tiếp xúc đồng đều và tránh sốc nhiệt. Các phương pháp cắt tiên tiến, chẳng hạn như cưa dây kim cương với tốc độ tiến dao được tối ưu hóa, giảm thiểu các vết nứt nhỏ và hư hỏng cạnh có thể dẫn đến bề mặt không bằng phẳng.

3. Mài có kiểm soát

Quá trình mài được thực hiện để đạt được độ dày mục tiêu và cải thiện độ phẳng bề mặt. Mài hai mặt, trong đó cả hai mặt của tấm bán dẫn được xử lý đồng thời, đảm bảo việc loại bỏ vật liệu đồng đều. Kỹ thuật này giảm thiểu độ cong và giảm căng thẳng dư thừa. Máy mài hiện đại sử dụng cài đặt tốc độ và áp suất do máy tính điều khiển để đạt được kết quả nhất quán trên nhiều tấm bán dẫn.

4. Kỹ thuật đánh bóng

Đánh bóng là một bước quan trọng để đạt được độ phẳng quang học. Đánh bóng cơ học hóa học kết hợp mài mòn cơ học với các phản ứng hóa học để tạo ra các bề mặt siêu phẳng. Quá trình đánh bóng phải được theo dõi cẩn thận để tránh tạo ra những ứng suất mới. Các miếng đánh bóng và chế phẩm bùn được tối ưu hóa để loại bỏ vật liệu đồng đều, đảm bảo rằng bề mặt tấm wafer vẫn nằm trong dung sai độ phẳng được chỉ định.

5. Giảm căng thẳng và rèn luyện

Xử lý nhiệt có thể làm giảm ứng suất bên trong tấm quang học. Ủ bao gồm việc làm nóng tấm bán dẫn đến nhiệt độ cụ thể và sau đó làm nguội từ từ. Quá trình này cho phép mạng tinh thể thư giãn, giảm độ cong và cong. Lịch trình ủ thích hợp là rất quan trọng, vì quá trình gia nhiệt quá mức hoặc không đồng đều có thể làm trầm trọng thêm các vấn đề về độ phẳng.

6. Đo lường và kiểm tra

Việc đo chính xác độ phẳng của tấm wafer là điều cần thiết để giám sát chất lượng chế tạo. Giao thoa kế, đo biên dạng và quét laser là những kỹ thuật thường được sử dụng để phát hiện sai lệch ở cấp độ micromet hoặc dưới micromet. Việc phát hiện sớm các vấn đề về độ phẳng cho phép thực hiện các hành động khắc phục, chẳng hạn như đánh bóng bổ sung hoặc loại bỏ vật liệu có chọn lọc, trước khi tấm bán dẫn tiến tới các giai đoạn chế tạo tiếp theo.

7. Kiểm soát môi trường

Duy trì một môi trường chế tạo ổn định là rất quan trọng để duy trì độ phẳng của tấm bán dẫn. Phòng sạch có nhiệt độ và độ ẩm được kiểm soát sẽ giảm nguy cơ giãn nở nhiệt và cong vênh do độ ẩm. Bệ chống rung và hệ thống lưu trữ được thiết kế cẩn thận ngăn ngừa biến dạng cơ học trong quá trình xử lý và vận chuyển.

Những thách thức trong việc duy trì độ phẳng

Mặc dù có các kỹ thuật tiên tiến nhưng vẫn tồn tại một số thách thức trong việc đảm bảo độ phẳng của tấm bán dẫn quang học. Đường kính tấm bán dẫn cao làm tăng khả năng bị uốn cong, vì các tấm bán dẫn lớn hơn có độ dốc ứng suất lớn hơn. Tấm wafer mỏng dễ bị uốn cong dưới trọng lượng của chính chúng hoặc trong quá trình xử lý. Hơn nữa, các hình học wafer phức tạp, chẳng hạn như các wafer có hoa văn hoặc được phủ, có thể tạo ra các điểm ứng suất cục bộ làm ảnh hưởng đến độ phẳng.

Một thách thức khác là sự cân bằng giữa độ phẳng bề mặt và tốc độ loại bỏ vật liệu. Quá trình mài và đánh bóng mạnh có thể tăng năng suất nhưng có thể gây ra ứng suất vi mô. Cân bằng năng suất với các yêu cầu về độ chính xác cao vẫn là vấn đề quan trọng mà các nhà sản xuất phải cân nhắc.

Những tiến bộ trong kiểm soát độ phẳng

Những tiến bộ công nghệ gần đây đã cải thiện khả năng đạt được các tấm quang học siêu phẳng. Hệ thống giám sát thời gian thực theo dõi việc loại bỏ vật liệu trong quá trình mài và đánh bóng, cho phép điều chỉnh tự động để duy trì độ phẳng. Kỹ thuật đánh bóng thích ứng, thay đổi áp suất và dòng chảy bùn một cách linh hoạt, bù đắp cho sự thay đổi độ dày cục bộ. Ngoài ra, những tiến bộ trong kỹ thuật liên kết tấm bán dẫn và chất nền làm giảm biến dạng do ứng suất gây ra trong các tấm bán dẫn quang tổng hợp.

Những cân nhắc thực tế cho nhà sản xuất

Đối với các nhà sản xuất, việc đảm bảo độ phẳng của tấm bán dẫn là một quy trình gồm nhiều bước đòi hỏi sự tích hợp trên tất cả các giai đoạn chế tạo. Từ việc lựa chọn các bó pha lê chất lượng cao cho đến việc cắt, mài, đánh bóng và giảm căng thẳng chính xác, mỗi bước đều góp phần tạo nên độ phẳng cuối cùng. Việc kiểm tra liên tục và kiểm soát môi trường cũng rất cần thiết để duy trì tính nhất quán giữa các lô sản xuất.

Đầu tư vào thiết bị có độ chính xác cao và nhân sự được đào tạo là điều cần thiết để đạt được độ phẳng mong muốn. Các giao thức được tiêu chuẩn hóa và tuân thủ các thông số kỹ thuật về độ phẳng đảm bảo rằng các tấm bán dẫn đáp ứng các yêu cầu về hiệu suất cho các ứng dụng quang học cao cấp.

Phần kết luận

Độ phẳng trong chế tạo tấm bán dẫn quang học là thông số chất lượng cơ bản ảnh hưởng đến hiệu suất của các thiết bị và hệ thống quang học. Để đạt được và duy trì độ phẳng đòi hỏi phải chú ý cẩn thận đến việc lựa chọn vật liệu, gia công cơ khí, xử lý nhiệt và kiểm soát môi trường. Kỹ thuật đo lường tiên tiến và xử lý thích ứng nâng cao hơn nữa khả năng sản xuất các tấm bán dẫn đáp ứng các yêu cầu nghiêm ngặt về độ phẳng.

Hiểu các yếu tố ảnh hưởng đến độ phẳng và thực hiện các quy trình kiểm tra và chế tạo mạnh mẽ là điều cần thiết đối với các nhà sản xuất và nhà nghiên cứu làm việc với tấm bán dẫn quang học. Bằng cách ưu tiên độ phẳng, các tấm bán dẫn quang học có thể đáp ứng một cách đáng tin cậy nhu cầu có độ chính xác cao của quang tử học, hệ thống laser và ứng dụng cảm biến quang học hiện đại.

32041102000130

32041102000130